April 2013

A Publication of SIGAda,

the ACM Special Interest Group on Ada

#### **Table of Contents**

| 3        |

|----------|

| 4        |

| 6        |

|          |

| 9        |

|          |

| 15       |

| 24       |

| 32       |

| 32<br>45 |

| 43       |

| 53       |

|          |

| 64       |

| 84       |

| 93       |

| 101      |

| 116      |

| 116      |

| 128      |

| 134      |

|          |

| 138      |

|          |

| 146      |

|          |

| 150      |

|          |

|          |

|          |

| 157      |

| 169      |

| 180      |

| 182      |

|          |

## ACM Digital Library

www.acm.org/dl

## The Ultimate Online INFORMATION TECHNOLOGY Resource!

Powerful and vast in scope, the **ACM Digital Library** is the ultimate online resource offering unlimited access and value!

The **ACM Digital Library** interface includes:

- The ACM Digital Library offers over 45 publications including all ACM journals, magazines, and conference proceedings, plus vast archives, representing over two million pages of text. The ACM DL includes full-text articles from all ACM publications dating back to the 1950s, as well as third-party content with selected archives. www.acm.org/dl

- The Guide to Computing Literature offers an enormous bank of more than one million bibliographic citations extending far beyond ACM's proprietary literature, covering all types of works in computing such as journals, proceedings, books, technical reports, and theses! www.acm.org/guide

- The Online Computing Reviews Service includes reviews by computing experts, providing timely commentary and critiques of the most essential books and articles.

Available only to ACM Members.

Join ACM online at www.acm.org/joinacm

To subscribe to the ACM Digital Library, contact ACM Member Services:

Phone: 1.800.342.6626 (U.S. and Canada)

+1.212.626.0500 (Global)

Fax: +1.212.944.1318 Hours: 8:30 a.m.-4:30 p.m., Eastern Time

Email: acmhelp@acm.org

Mail: ACM Member Services

General Post Office

PO Box 30777

New York, NY 10087-0777 USA

ACM Professional Members can add the ACM Digital Library for only \$99 (USD). Student Portal Package membership includes the Digital Library. Institutional, Corporate, and Consortia Packages are also available.

Association for Computing Machinery

Advancing Computing as a Science & Profession

AD10

# join today! SIGAda & ACM

www.acm.org/sigada

www.acm.org

The **ACM Special Interest Group on Ada Programming Language** (SIGAda) provides a forum on all aspects of the Ada language and technologies, including usage, education, standardization, design methods, and compiler implementation. Among the topics that SIGAda addresses are software engineering practice, real-time applications, high-integrity & safety-critical systems, object-oriented technology, software education, and large-scale system development. SIGAda explores these issues through an annual international conference, special-purpose Working Groups, active local chapters, and its *Ada Letters* publication.

The **Association for Computing Machinery** (ACM) is an educational and scientific computing society which works to advance computing as a science and a profession. Benefits include subscriptions to *Communications of the ACM, MemberNet, TechNews* and *CareerNews*, full and unlimited access to online courses and books, discounts on conferences and the option to subscribe to the ACM Digital Library.

| SIGAda (ACM Member)                                                             | \$ 25 |

|---------------------------------------------------------------------------------|-------|

| SIGAda (ACM Student Member & Non-ACM Student Member)                            | \$ 10 |

| SIGAda (Non-ACM Member)                                                         | \$ 25 |

| ACM Professional Membership (\$99) & SIGAda (\$25)                              | \$124 |

| ACM Professional Membership (\$99) & SIGAda (\$25) & ACM Digital Library (\$99) | \$223 |

| ACM Student Membership (\$19) & SIGAda (\$10)                                   | \$ 29 |

| Ada Letters only                                                                | \$ 53 |

| Expedited Air for Communications of the ACM (outside N. America)                | \$ 58 |

### payment information

addresses remain strictly confidential. Check one of the following if

☐ ACM and other sister society announcements

☐ ACM subscription and renewal notices only

you wish to restrict the use of your name:

☐ ACM announcements only

| Name                                                                                                                                                                    | Credit Card Type: ☐ AMEX ☐ VISA ☐ MC                                                                                                                                                                                                                                                                       |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| ACM Member #                                                                                                                                                            | Credit Card #                                                                                                                                                                                                                                                                                              |  |  |

| Mailing Address                                                                                                                                                         | Exp. Date                                                                                                                                                                                                                                                                                                  |  |  |

|                                                                                                                                                                         | Signature                                                                                                                                                                                                                                                                                                  |  |  |

| City/State/Province                                                                                                                                                     | <ul> <li>Make check or money order payable to ACM, Inc</li> <li>ACM accepts U.S. dollars or equivalent in foreign currency. Prices include surface delivery charge. Expedited Air Service, which is a partial air freight delivery service, is available outside North America. Contact ACM for</li> </ul> |  |  |

| ZIP/Postal Code/Country                                                                                                                                                 |                                                                                                                                                                                                                                                                                                            |  |  |

| Email                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                            |  |  |

| Mobile Phone                                                                                                                                                            |                                                                                                                                                                                                                                                                                                            |  |  |

| Fax                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                            |  |  |

| Mailing List Restriction  ACM occasionally makes its mailing list available to computer-related organizations, educational institutions and sister societies. All email | Questions? Contact:  ACM Headquarters  ACM                                                                                                                                                                                                                                                                 |  |  |

General Post Office P.O. Box 30777

New York, NY 10087-0777

SIGAPP

www.acm.org/joinsigs

2 Penn Plaza, Suite 701

New York, NY 10121-0701

voice: 212-626-0500

fax: 212-944-1318

email: acmhelp@acm.org

Advancing Computing as a Science & Profession

#### Volume XXXIII Number 1, April 2013

#### **Table of Contents**

| Newsletter Information                                                                                                                                                             |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| From the Editor's Desk                                                                                                                                                             | 3   |

| Editorial Policy                                                                                                                                                                   | 4   |

| Key Contacts                                                                                                                                                                       | 6   |

| IRTAW-15 Workshop Papers                                                                                                                                                           |     |

| Support for Multiprocessor Platforms - A. Burns and A.J. Wellings TTF-Ravenscar: A Profile to Support Reliable High-Integrity Multiprocessor Ada Applications -                    | 9   |

| A. Burns, A.J. Wellings and A.H. Malik                                                                                                                                             | 15  |

| An EDF Run-Time Profile based on Ravenscar - A. Burns                                                                                                                              | 24  |

| Ada 2012: Resource Sharing and Multiprocessors - S. Lin, A.J. Wellings and A. Burns                                                                                                | 32  |

| Going real-time with Ada 2012 and GNAT - Jose F. Ruiz                                                                                                                              | 45  |

| Adapting the end-to-end flow model for distributed Ada to the Ravenscar profile -                                                                                                  |     |

| Héctor Pérez Tijero, J. Javier Gutiérrez, and Michael González Harbour                                                                                                             | 53  |

| Charting the evolution of the Ada Ravenscar code archetypes - Marco Panunzio and Tullio Vardanega                                                                                  | 64  |

| Revisiting Transactions in Ada - Antonio Barros and Luis Miguel Pinho                                                                                                              | 84  |

| Deferred Setting of Scheduling Attributes in Ada 2012 - Sergio Saez and Alfons Crespo                                                                                              | 93  |

| Programming Language Vulnerabilities - Proposals to Include Concurrency Paradigms - Stephen Michell Adding Multiprocessor and Mode Change Support to the Ada Real-Time Framework - | 101 |

| Sergio Saez, Jorge Real, and Alfons Crespo                                                                                                                                         | 116 |

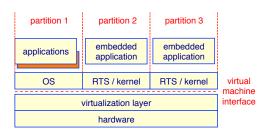

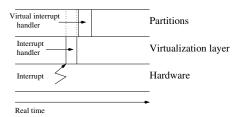

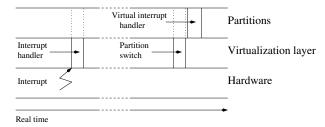

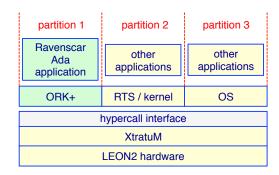

| Ada Real-Time Services and Virtualization - Juan Zamorano, Angel Esquinas and Juan A. de la Puente                                                                                 | 128 |

| Session Summary: Multiprocessor Issues, Part 1 Chair: Jorge Real and Rapporteur: Jose F. Ruiz                                                                                      | 134 |

| Session Summary: Multiprocessor Issues, Part 2 (Resource Control Protocols)                                                                                                        | 138 |

| Chair: Andy Wellings and Rapporteur: Luís Miguel Pinho                                                                                                                             |     |

| Session Summary: Language Profile and Application Frameworks Chair: Alan Burns and Rapporteur: Tullio Vardanega                                                                    | 146 |

| Session Summary: Concurrency Issues                                                                                                                                                | 150 |

| Chair: Juan Antonio de la Puente and Rapporteur: Stephen Michell                                                                                                                   |     |

| Other Research Papers                                                                                                                                                              |     |

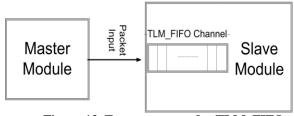

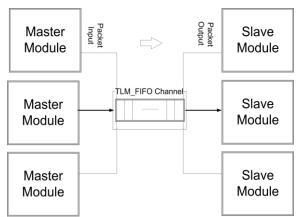

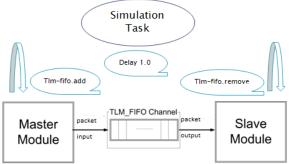

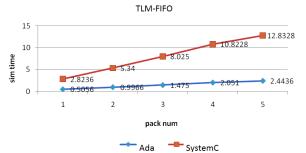

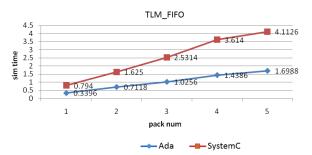

| Investigating SystemAda: TLM_FIFO Detailed Characteristics Proof, TLM2.0 Interfaces Implementation, Simulation Time Comparison to SystemC - Negin Mahani                           | 157 |

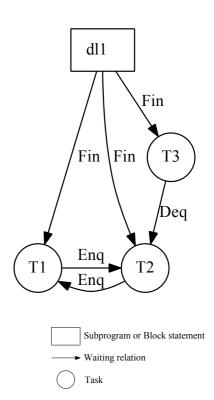

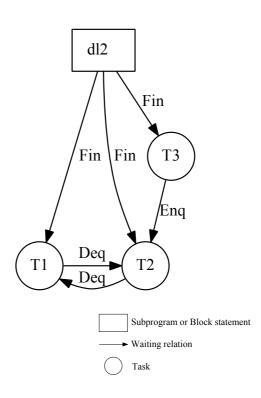

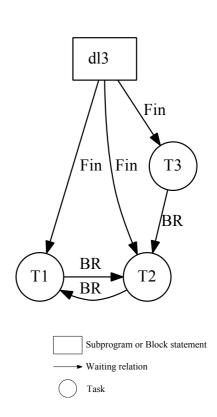

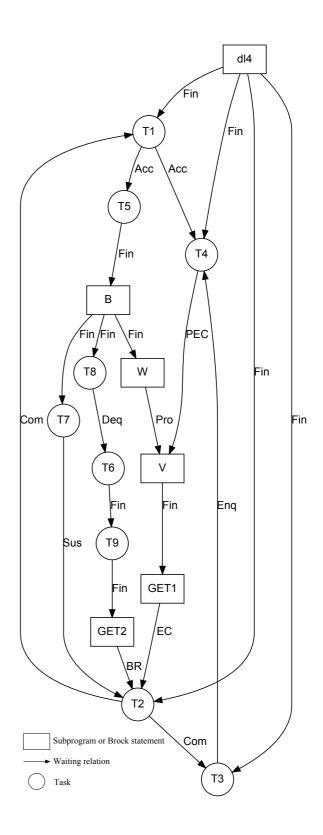

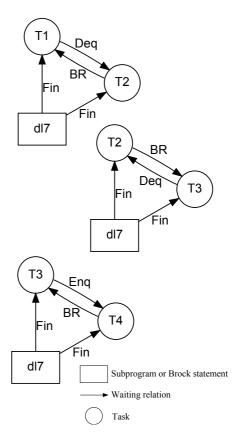

| New Types of Tasking Deadlocks in Ada 2012 Programs - Takeo Ekiba, Yuichi Goto, and Jingde Cheng                                                                                   | 169 |

| Ada Europe Conference 2013                                                                                                                                                         | 180 |

| SIGAda 2013 Conference                                                                                                                                                             | 182 |

#### **CHAIR**

Ricky E. Sward, The MITRE Corporation, 1155 Academy Park Loop Colorado Springs, CO 80910 USA

Phone: +1 (719) 572-8263, RSward@Mitre.org

#### VICE-CHAIR FOR MEETINGS AND CONFERENCES

Alok Srivastava, TASC Inc., 475 School Street SW, Washington, DC 20024-2711 USA

Phone: +1 (202) 314-1419, Alok.Srivastava@TASC.Com

#### VICE-CHAIR FOR LIAISON

Greg Gicca, AdaCore, 1849 Briland Street, Tarpon Springs, FL 34689, USA

Phone: +1 (646) 375-0734, Gicca@AdaCore.Com

#### **SECRETARY**

Clyde Roby, Institute for Defense Analyses, 4850 Mark Center Drive, Alexandria, VA 22311 USA

Phone: +1 (703) 845-6666, Roby@ida.org

#### **TREASURER**

Geoff Smith, Lightfleet Corporation, PO Box 6256, Aloha, OR 97007, USA

Phone: +1 (360) 816-2821, GSmith@Lightfleet.Com

#### INTERNATIONAL REPRESENTATIVE

Dirk Craeynest, c/o K.U.Leuven, Dept. of Computer Science, Celestijnenlaan 200-A, B-3001 Leuven (Heverlee) Belgium, Dirk.Craeynest@cs.kuleuven.be

#### **PAST CHAIR**

John W. McCormick, Computer Science Department, University of Northern Iowa, Cedar Falls, IA 50614, USA Phone: +1 (319) 273-6056, McCormick@cs.uni.edu

#### ACM PROGRAM COORDINATOR SUPPORTING SIGAda

Irene Frawley, 2 Penn Plaza, Suite 701, New York, NY 10121-0701

Phone: +1 (212) 626-0605, Frawley@ACM.Org

#### For advertising information contact:

Advertising Department

2 Penn Plaza, Suite 701, New York, NY 10121-0701

Phone: (212) 869-7440; Fax (212) 869-0481

Is your organization recognized as an Ada supporter? Become a SIGAda INSTITUTIONAL SPONSOR! Benefits include having your organization's name and address listed in every issue of Ada Letters, two subscriptions to Ada Letters and member conference rates for all of your employees attending SIGAda events. To sign up, contact Rachael Barish, ACM Headquarters, 2 Penn Plaza, Suite 701, New York, NY 10121-0701, and email: MEETING@ACM.ORG, Phone: 212-626-0603.

Interested in reaching the Ada market? Please contact Jennifer Booher at Worldata (561) 393-8200 Ext. 131, email: platimer@worldata.com. Please make sure to ask for more information on ACM membership mailing lists and labels.

Ada Letters (ISSN 1094-3641) is published three times a year by the Association for Computing Machinery, 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA. The basic annual subscription price is \$20.00 for ACM members.

POSTMASTER: Send change of address to Ada Letters:

ACM, 2 Penn Plaza, Suite 701, New York, NY 10121-0701 USA

#### **Notice to Past Authors of ACM-Published Articles**

ACM intends to create a complete electronic archive of all articles and/or other material previously published by ACM. If you have written a work that has been previously published by ACM in any journal or conference proceedings prior to 1978, or any SIG Newsletter at any time, and you do NOT want this work to appear in the ACM Digital Library, please inform <a href="mailto:permissions@acm.org">permissions@acm.org</a>, stating the title of the work, the author(s), and where and when published.

#### From the Editor's Desk

#### Alok Srivastava

Welcome to this issue of ACM Ada Letters. In this issue you will find very remarkable papers presented at 15th International Real-Time Ada Workshop (IRTAW-15) in Liébana (Cantabria), Spain. Since the late Eighties the International Real-Time Ada Workshop series has provided a forum for identifying issues with real-time system support in Ada and for exploring possible approaches and solutions, and has attracted participation from key members of the research, user, and implementer communities worldwide. Recent IRTAW meetings have significantly contributed to the Ada 2005 standard and to the proposals for Ada 2012, especially with respect to the tasking features, the real-time and high-integrity systems annexes, and the standardization of the Ravenscar profile. The summary and outcome of various focused sessions during the IRTAW-15 are listed here.

In this issue you will find the Call for Technical Contributions for the High-Integrity Language Technology SIGAda 2013 conference to be held from November 10-14, 2013 in Pittsburgh, Pennsylvania (USA). The conference will feature three outstanding keynote speakers Edmund M. Clarke from Carnegie Mellon University and 2007 ACM Turing Award winner, Jeannette Wing from Microsoft Research and Ada veteran John Goodenough from Software Engineering Institute. Another major Ada event, the 18th International Conference on Reliable Software Technologies Ada-Europe 2013 to be held from June 10 to14, 2013 in Berlin, Germany.

In this issue you will also find one very interesting research paper "Investigating SystemAda: TLM\_FIFO Detailed Characteristics Proof, TLM2.0 Interfaces Implementation, Simulation Time Comparison to SystemC" by our regular contributor Negin Mahani. In another paper by Takeo Ekiba, Yuichi Goto, and Jingde Cheng from Saitama University, Japan have presented some new types of tasking deadlocks concerning the new synchronization waiting relations defined in the Ada 2012.

Ada Letters is a great place to submit articles of your experiences with the language revision, tips on usage of the new language features, as well as to describe success stories using Ada. We'll look forward to your submission. You can submit either a MS Word or Adobe PDF file (with 1" margins and no page numbers) to our technical editor:

Pat Rogers, Ph.D. AdaCore, 207 Charleston, Friendswood, TX 77546 (USA) +1 281 648 3165, Rogers@AdaCore.Com

We look forward to hearing from you!

Alok Srivastava, Ph.D. Technical Fellow, TASC Inc. 475 School St, SW; Washington, DC 20024 (USA) +1 202 314 1419 Alok.Srivastava@TASC.Com Editorial Policy (from Alok Srivastava, Managing Editor)

As the editor of ACM Ada Letters, I'd like to thank you for your continued support to ACM SIGAda, R&D in the areas of High Reliability and Safety Critical Software Development and encourage you to submit articles for publication. In addition, if there is some way we can make **ACM Ada\_Letters** more useful to you, please let me know. Note that Ada Letters is now on the web! See <a href="http://www.acm.org/sigada/ada\_letters/index.html">http://www.acm.org/sigada/ada\_letters/index.html</a>. The two newest issues are available only to SIGAda members. Older issues beginning March 2000 are available to all.

Now that Ada is standing on its own merits without the support of the DoD, lots of people and organizations have stepped up to provide new tools, mechanisms for compiler validation/assessment, and standards (especially ASIS). The Ada 2012 language version is fulfilling the market demand of robust safety and security elements and thereby generating a new enthusiasm into the software development. Ada Letters is a venue for you to share your successes and ideas with others in the Ada and specifically in High Reliability Safety Critical Software Development community. Be sure to take advantage of it so that we can all benefit from each other's learning and experience.

As some of the other ACM Special Interest Group periodicals have moved, Ada Letters also transitioned to a **tri-annual publication**. With exception of special issues, Ada Letters now is going to be published three times a year, with the exception of special issues. The revised schedules and submission deadlines are as follows:

| Deadline                        | Issue        | Deadline                       | Issue          |

|---------------------------------|--------------|--------------------------------|----------------|

| June 1 <sup>st</sup> , 2013     | August, 2013 | October 1 <sup>st</sup> , 2013 | December, 2013 |

| February 1 <sup>st</sup> , 2014 | April, 2014  | June 1 <sup>st</sup> , 2014    | August, 2014   |

#### Please send your article to Dr. Pat Rogers at rogers@adacore.com

#### **Guidelines for Authors**

Letters, announcements and book reviews should be sent directly to the Managing Editor and will normally appear in the next corresponding issue.

Proposed articles are to be submitted to the Technical Editor. Any article will be considered for publication, provided that topic is of interest to the SIGAda membership. Previously published articles are welcome, provided the previous publisher or copyright holder grants permission. In particular, keeping with the theme of recent SIGAda conferences, we are interested in submissions that demonstrate that "Ada Works." For example, a description of how Ada helped you with a particular project or a description of how to solve a task in Ada are suitable.

Although Ada Letters is not a refereed publication, acceptance is subject to the review and discretion of the Technical Editor. In order to appear in a particular issue, articles must be submitted far enough in advance of the deadline to allow for review/edit cycles. Backlogs may result in an article's being delayed for two or more issues. Contact the Managing Editor for information on the current publishing queue.

Articles should be submitted electronically in one of the following formats: MS Word (preferred) Postscript, or Adobe Acrobat. All submissions must be formatted for US Letter paper (8.5" x 11") with one inch margins on each side (for a total print area of 6.5" x 9") with no page numbers, headers or footers. Full justification of text is preferred, with proportional font (preferably Times New Roman, or equivalent) of no less than 10 points. Code insertions should be presented in a non-proportional font such as Courier.

The title should be centered, followed by author information (also centered). The author's name, organization name and address, telephone number, and e-mail address should be given. For previously published articles, please give an introductory statement (in a distinctive font) or a footnote on the first page identifying the previous publication. ACM is improving member services by creating an electronic library of all of its publications. Read the following for how this affects your submissions.

#### **Notice to Contributing Authors to SIG Newsletters:**

By submitting your article for distribution in this Special Interest Group publication, you hereby grant to ACM the following non-exclusive, perpetual, worldwide rights:

- to publish in print on condition of acceptance by the editor

- to digitize and post your article in the electronic version of this publication

- to include the article in the ACM Digital Library

- to allow users to copy and distribute the article for noncommercial, educational or research purposes

However, as a contributing author, you retain copyright to your article and ACM will make every effort to refer requests for commercial use directly to you.

#### **Notice to Past Authors of ACM-Published Articles**

ACM intends to create a complete electronic archive of all articles and/or other material previously published by ACM. If you have a work that has been previously published by ACM in any journal or conference proceedings prior to 1978, or any SIG Newsletter at any time, and you do NOT want this work to appear in the ACM Digital Library, please inform permissions@acm.org, stating the title of the work, the author(s), and where and when published.

#### **Back Issues**

Back issues of Ada Letters can be ordered at the price of \$6.00 per issue for ACM or SIGAda members; and \$9.00 per issue for non-ACM members. Information on availability, contact the ACM Order Department at 1-800-342-6626 or 410-528-4261. Checks and credit cards only are accepted and payment must be enclosed with the order. Specify volume and issue number as well as date of publication. Orders must be sent to:

ACM Order Department, P.O. Box 12114, Church Street Station, New York, NY 10257 or via FAX: 301-528-8550.

#### **KEY CONTACTS**

#### **Technical Editor**

Send your book reviews, letters, and articles to:

Pat Rogers AdaCore 207 Charleston Friendswood, TX 77546 +1-281-648 3165

Email: rogers@adacore.com

#### **Managing Editor**

Send announcements and short notices to:

Alok Srivastava TASC Inc. 475 School Street, SW Washington DC 20024 +1-202-314-1419

Email: Alok.Srivastava@tasc.com

#### Advertising

Send advertisements to:

William Koonev Advertising/Sales Account Executive 2 Penn Plaza, Suite 701 New York, NY 10121-0701 Phone: +1-212-869-7440

Fax: +1-212-869-0481

#### **Local SIGAda Matters**

Send Local SIGAda related matters to:

Greg Gicca AdaCore 1849 Briland Street Tarpon Springs, FL 34689, USA Phone: +1-646-375-0734

Fax: +1-727-944-5197 Email: Gicca@AdaCore.Com

#### Ada CASE and Design Language Developers

Send ADL and CASE product Info to:

Judy Kerner The Aerospace Corporation Mail Stop M8/117 P.O. Box 92957 Los Angeles, CA 90009 +1-310-336-3131 Email: kerner@aero.org

#### **Ada Around the World**

Send Foreign Ada organization info to:

Dirk Craeynest c/o K.U.Leuven, Dept. of Computer Science, Celestijnenlaan 200-A, B-3001 Leuven (Heverlee)

Email: Dirk.Craeynest@cs.kuleuven.be

#### **Reusable Software Components**

Send info on reusable software to:

Trudy Levine Computer Science Department Fairleigh Dickinson University Teaneck, NJ 07666 +1-201-692-2000

Email: levine@fdu.edu

#### SIGAda Working Group (WG) Chairs

See <a href="http://www.acm.org/sigada/">http://www.acm.org/sigada/</a> for most up-to-date information

#### Ada Application Programming Interfaces WG

Geoff Smith Lightfleet Corporation 4800 NW Camas Meadows Drive Camas, WA 98607

Phone: +1-503-816-1983 Fax: +1-360-816-5750

Email: gsmith@lightfleet.com

#### Ada Semantic Interface Specification WG

http://www.acm.org/sigada/wg/asiswg/asiswg.html

Bill Thomas

The MITRE Corp

7515 Colshire Drive

McLean, VA 22102-7508

Phone: +1-703-983-6159 Fax: +1-703-983-1339

Email: BThomas@MITRE.Org

#### **Education WG**

http://www.sigada.org/wg/eduwg/eduwg.html Mike Feldman 420 N.W. 11th Ave., #915 Portland, OR 97209-2970

Email: MFeldman@seas.gwu.edu

#### Standards WG

Robert Dewar 73 5th Ave. New York, NY 10003

Phone: +1-212-741-0957 Fax: +1-232-242-3722 Email: dewar@cs.nyu.edu

#### Ada Around the World

#### (National Ada Organizations)

From: <a href="http://www.ada-europe.org/members.html">http://www.ada-europe.org/members.html</a>

#### Ada-Europe

Tullio Vardanega University of Padua Department of Pure and Applied Mathematics Via Trieste 63 I-35121, Padova, Italy

Phone: +39-049-827-1359 Fax: +39-049-827-1444

E-mail: tullio.vardanega@math.unipd.it

http://www.ada-europe.org/

#### **Ada-Belgium**

Dirk Craeynest C/o K.U.Leuven. D

C/o K.U.Leuven, Dept. of Computer Science, Celestijnenlaan 200-A, B-3001 Leuven (Heverlee), Belgium

Phone: +32-2-725 40 25 Fax : +32-2-725 40 12

E-mail: Dirk.Craeynest@cs.kuleuven.be http://www.cs.kuleuven.be/~dirk/ada-

belgium/

#### Ada in Denmark

Jørgen Bundgaard E-mail: Info at Ada-DK.org http://www.Ada-DK.org/

#### **Ada-Deutschland**

Peter Dencker, Steinackerstr. 25 D-76275 Ettlingen-Spessartt, Germany E-mail: dencker@parasoft.de http://www.ada-deutschland.de/

#### Ada-France

Association Ada-France c/o Jérôme Hugues Département Informatique et Réseau École Nationale Supérieure des Télécommunications, 46, rue Barrault 75634 Paris Cedex 135, France E-mail: bureau@ada-france.org http://www.ada-france.org/

#### Ada Spain

J. Javier Gutiérrez

P.O. Box 50.403

E-28080 Madrid, Spain

Phone: +34-942-201394

Fax : +34-942-201402

E-mail: gutierjj@unican.es

http://www.adaspain.org/

#### Ada in Sweden

Rei Stråhle Box Saab Systems S:t Olofsgatan 9A

SE-753 21 Uppsala, Sweden Phone: +46-73-437-7124 Fax : +46-85-808-7260

E-mail: Rei.Strahle@saabgroup.com

http://www.ada-i-sverige.se/

#### Ada in Switzerland

Ahlan Marriott White Elephant GmbH Postfach 327

CH-8450 Andelfingen, Switzerland

Phone: +41 52 624 2939 Fax : +41 52 624 2334

E-mail: ada@white-elephant.ch http://www.ada-switzerland.org/

#### Italy

Contact: tullio.vardanega@math.unipd.it

#### Ada-Europe Secretariat

e-mail: secretariat@ada-europe.org

#### **Support for Multiprocessor Platforms**

A. Burns and A.J. Wellings Department of Computer Science University of York, UK

burns@cs.york.ac.uk, andy@cs.york.ac.uk

#### **Abstract**

Multiprocessor platforms are becoming the norm for more powerful embedded real-time systems. Although Ada allows its tasks to be executed on such platforms, until recently it has provided no explicit support. The new revision of Ada now provides facilities for allocating and scheduling tasks on SMP platforms. The notions of a CPU and Dispatching-Domain have been introduced. We summaries these facilities and review the extra support that could be provided in the future for SMP and non-SMP platforms.

#### 1 Introduction

The support that Ada provides, or should provide, for programs executing on multiprocessor or multicore platforms has been the subject of a number of IRTAW papers [11, 10, 6, 12, 8] and discussion sessions [7, 5] at the last two workshops. This is in addition to the many papers there have been, since the very first workshop, on distributed systems.

At the last workshop a number of recommendation were made for extensions to be included in the current revision to the Ada standard. Many, but not all, of these suggestions have been incorporated into the draft language definition that is currently been finalised. In this paper we briefly review the features that will be supported in Ada 2012, and revisit the many other topics that have been discussed previously but have are not made it into the Standard. Our aim is to inform a possible workshop discussion on what should be included in future amendments of the language, and what features might better be addressed by other formal or defacto standards.

#### 2 Basic Requirements

The primary requirement for supporting the execution of Ada tasks on symmetric multiprocessors (SMPs) is to manage the mapping of tasks to processors [4]. We assume that we are concerned with real-time code, in which case the execution of any task can be view as a sequence of invocations or *jobs*. Between jobs, the task is blocked, waiting either for an event (typically an external interrupt) or for a future time instance. In this paper we do not discuss support for resource sharing between jobs. This topic is discussed in depth in an accompanying paper to the workshop.

To cater for the allocation/mapping of tasks/jobs to processors, two basic approaches are possible:

- 1. Fully Partitioned each task is allocated to a single processor on which all its jobs must run; and

- 2. Global all tasks/jobs can run on all processors, jobs may migrate during execution.

There are many motivation for choosing either global or partitioned allocation, some of these motivations come from issues of scheduling [2]. These details are not significant here, what is important is that the Ada language is able to support both schemes.

From these schemes, two further variants are commonly discussed: for global scheduling, tasks are restricted to a subset of the available CPUs; and for partitioned scheduling, the program can explicitly change a task's affinity and hence cause it to be moved at run-time.

Restricting the set of CPUs on which a task can be globally scheduled supports scalability – as platforms move to contain hundreds of CPUs, the overheads of allowing full task migration become excessive and outweighs any advantage that might accrue from global scheduling. Controlled changing of a task's affinity has been shown to lead to improved schedulability for certain types of application [9, 1, 3].

In the following discussions, in keeping with the terminology in the new Ada Standard, we will use the term *dispatching domain* to represent a group of processors across which global scheduling occurs. A task is said to be assigned to a dispatching domain and may also be restricted to a particular CPU.

For non-SMPs there are many other issues to consider. For cc-NUMA architectures these include the memory map, partitioning of the heap and control over object location. We will return to these issues in Section 4.2.

#### 3 Features in Ada 2012

The following packages allows the group of CPUs to be partitioned into a finite set of non-overlapping 'Dispatching Domains'. One dispatching domain is defined to be the 'System' dispatching domain; the environmental task and any derived from that task are allocated to the 'System' dispatching domain. Subprograms are defined to allow new dispatching domains to be created.

Tasks can be assigned to a dispatching domain and be globally scheduled within that dispatching domain; alternatively they can be assigned to a dispatching domain and restricted to a specific CPU within that dispatching domain. Tasks cannot be assigned to more than one dispatching domain, or restricted to more than one CPU.

The first package just defines a parent unit for all microprocessor facilities, and give a range for an integer representation of each CPU. Note the value 0 is used to indicate Not\_A\_Specific\_CPU; so the CPUs are actually numbered from one. The function Number\_Of\_CPUs will, for any execution of the program, return the same value. In effect the number of CPUs is a constant and reflects the number of available processors at system start up.

```

package System.Multiprocessors is

pragma Preelaborate(Multiprocessors);

type CPU_Range is range 0 .. <implementation-defined>;

Not_A_Specific_CPU : constant CPU_Range := 0;

subtype CPU is CPU_Range range 1 .. CPU_Range'Last;

function Number_Of_CPUs return CPU;

end System.Multiprocessors;

```

The second package provides the support for dispatching domains.

```

with Ada.Real_Time;

package System.Multiprocessors.Dispatching_Domains is

pragma Preelaborate(Dispatching_Domains);

Dispatching_Domain_Error : exception;

type Dispatching_Domain (<>) is limited private;

System_Dispatching_Domain : constant Dispatching_Domain;

-- initially all CPUs are in System_Dispatching_Domain

function Create(First, Last : CPU) return Dispatching_Domain;

- removes specified CPUs from System_Dispatching_Domain

function Get_First_CPU(Domain : Dispatching_Domain) return CPU;

function Get_Last_CPU(Domain : Dispatching_Domain) return CPU;

function Get_Dispatching_Domain(T : Task_Id := Current_Task)

return Dispatching_Domain;

procedure Assign_Task(Domain : in out Dispatching_Domain;

CPU : in CPU_Range := Not_A_Specific_CPU;

T : in Task Id := Current Task);

procedure Set_CPU(CPU : in CPU_Range; T : in Task_Id := Current_Task);

function Get_CPU(T : in Task_Id := Current_Task) return CPU_Range;

procedure Delay_Until_And_Set_CPU(

Delay_Until_Time : in Ada.Real_Time.Time; CPU : in CPU_Range);

... -- not specified by the language

end System.Multiprocessors.Dispatching_Domains;

```

The semantics of the features contained in this package are as one would expect, and are similar to those defined and recommended during the last IRTAW. However, it should be noted that a number of more general features identified during

the last workshop did not get included in the language amendment; in particular, the dispatching rules for each dispatching domain cannot be individually defined.

Although a pragma can be used to define CPU and Dispatching\_Domain:

```

pragma Dispatching_Domain(expression);

pragma CPU(expression);

for example,

task type T (Pri : System.Priority; Core : System.Multiprocessors.CPU) is

pragma Priority(Pri);

pragma CPU(Core);

pragma Dispatching_Domain(Hard_Real_Time);

entry SomeEntry(...); ...

end T:

```

where <code>Hard\_Real\_Time</code> is a defined <code>Dispatching\_Domain</code>, the use of such pragmas is now deprecated (deemed obsolescent) and <code>aspects</code> should be employed. The above code should now be written as:

```

task type T (Pri: System.Priority; Core : System.Multiprocessors.CPU) with

Priority => Pri,

CPU => Core,

Dispatching_Domain => Hard_Real_Time;

is

entry SomeEntry(...); ...

end T;

```

Although this is a quite difference syntactical form, there is no difference in semantics. With both forms a simple task declaration:

```

Example : T(13,3);

```

would place a task with priority 13 on CPU 3 within the Hard\_Real\_Time dispatching domain.

In addition to the above packages an extension to Ada.Interrupts (C.3.2) is made:

```

with System.Multiprocessors;

function Get_CPU(Interrupt: Interrupt_Id)

return System.Multiprocessors.CPU_Range;

```

Taken together the above set of facilities will allow multitasking Ada programs to be allocated and scheduled on to a basic multicore platform in which all cores are identical. Although each dispatching domain (DD) has the same dispatching (scheduling) rules, there is ample opportunity to program many different paradigms. For example, the range of priorities could be split between EDF and fixed priority (FP). In one DD only the EDF range is used, in another only the FP range. As a result, although the overall dispatching strategies are the same in each DD, in effect one DD is totally EDF scheduled (and could employ, for example, global partitioning) whilst the other is FP (and perhaps uses a fully partitioned approach).

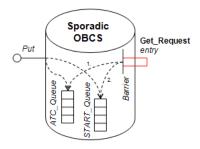

In addition to these facilities that are all focused on the control of task affinities, there is a new *task control barrier* package that allows a set of tasks to block on a condition and then be released in parallel. Such a facility is essential for many forms of data-centric parallelism (for example, a large array being searched by parallel tasks – one per core).

Finally, the definition of Volatile was clarified to enable lock-free synchronisation algorithms to be implemented.

#### 4 Review of Previous Suggestion

Here we review the suggestions that have been voiced at previous workshop, but which are not yet incorporated into Ada. We distinguish between SMPs and other more general platforms. In both of theses cases one of the issues that remain significant is the degree to which any of the Ada facilities can be efficiently mapped on to platforms that conform to standards provided by Posix or Linux. We do not however investigate this issue further here.

#### 4.1 SMP architectures

Two restrictions are apparent with the current proposal to extend the facilities provided in the Ada language for SMP platforms. One concerns the control over the number of CPUs, the other with control over scheduling. First the issue of the

number of CPUs and how they might map to dispatching domains. In the facilities described above, the set of CPUs is fixed and there is a static 'once and for all' allocation of CPUs to DDs.

Previously a more abstract API was proposed [11] in which sets of processors are defined with the availability of the CPUs potentially changing over time:

```

with Ada.Task_Identification; use Ada.Task_Identification;

package System.Processor_Elements is

Affinity_Error : exception;

Unsupported_Operation : exception;

type Processors is range 0 .. <<implementation-defined>>;

-- The number of processors available on this system.

-- Each processor has a logical Id in the range.

-- On a single processor system, the range is 0..0

type Processor_Set is array (Processors) of Boolean;

- A set of processors. A boolean set to True, indicates

-- that the logical processor is included in the set

function Available_Processors return Processor_Set;

-- Indicates which of the processors in the system are

-- current available to the program. In some

-- systems this will never change, others it may.

end System.Processor_Elements;

```

A package like this could support a more dynamic platform in which CPUs may alter their availability in a manner that would allow the programmer to produce adaptable code.

It was mentioned earlier that scheduling on a per-DD basis was consider at an earlier workshop – for example using code such as [4]:

```

with System; use System;

package Ada. Dispatching is

Dispatching_Policy_Error : exception;

type Dispatching_Domain_Policy is private.

type Scheme is (Priority Specific Dispatching,

Non_Preemptive_FIFO_Within_Priorities,

FIFO_Within_Priorities,

Round_Robin_Within_Priorities,

EDF_ACross_Priorities);

subtype Priority_Specific_Scheme is Scheme range

FIFO_Within_Priorities .. EDF_ACross_Priorities;

procedure Set_Policy(DDP : in out Dispatching_Domain_Policy;

P : Scheme):

procedure Set_Priority_Specific_Policy(

DDP : in out Dispatching_Domain_Policy;

P : Priority_Specific_Scheme;

Low: Priority; High: Priority);

-- raises Dispatching_Policy_Error if

-- DDP has not been set to Priority_Specific_Dispatching, or

-- High is not greater than Low, or

any priority from Low to High has already been set

private

-- not defined by language

end Ada.Dispatching;

```

However it is now not clear that this level of control over dispatching is needed and, as indicated above, sufficient flexibility can probably be extracted from the current facilities.

To support more stream-based parallelism, Ada 2012 has introduced the task control barrier. However further support is possible in this area. Ward and Audsley [10] argue for a broadcast primitive (to write to many protected objects in parallel),

and a new type of function for protected objects (POs). Such a function would have a barrier and hence could be blocked. But once the barrier is lowered all blocked function calls would proceed in parallel. In effect this would be a high level abstraction of the task control barrier; in a similar way that an ordinary PO is a more structured form of synchronous task control.

#### 4.2 Non-SMP architectures

Once the hardware platform can no longer be consider to be a pure SMP (where all processors are identical, work at the same speed and have the same relationship with memory) then many new challenges arise. The follow is a possible classification of such platform architectures:

- SMP-like processors are identical but run at different speeds,

- cc-NUMA cache-coherent Non Uniform Memory Architecture,

- NUMA no cache coherence, single address space,

- Heterogeneous multiple address spaces.

What can a future definition of Ada contain to help program applications for these emerging platforms?

For SMP-like, more knowledge about each processor needs to be available to the program. A simple ordering of CPU is insufficient. Some form of map must be provided and a representation beyond that of a simple integer will probably be required.

Wellings et al [12] investigated the needs of cc-NUMA. With this architecture, although there is cache coherence, the time it takes to access memory will vary significantly for different tasks/objects in the program. These access times must be managed for any real-time system. They concluded that at least four issues must be addressed:

- 1. understanding the address map,

- 2. using storage pools to partition the heap,

- 3. using representation aspects to control object location, and

- 4. using task affinities to control thread migration.

Once we move beyond cc-NUMA towards heterogenous processors and memory, the problems become more complex. With a single address space, regions of cache coherence must be identified and have some form of representation in the program. The partition model within Ada (primarily to support distributed systems) may have a role here. Once we have multiple address spaces then a 'distributed systems' model does seem appropriate. As assessment of the Ada partition model for such situations is necessary. Extensions may be required.

#### 5 Conclusions

In this paper we have attempted to review all the topics relating to multiprocessor platforms that were raised and discussed in previous workshops. We note the progress that has been made in the support that Ada now provides. But it is clear that for non-SMP architectures there are many challenges for any programming language that is attempting to support the production of efficient and predicable programs. Smart compilers might be able to remove some of these problems, but it is likely that some abstract representation of the platform will need to be available at the code level.

#### References

- [1] B. Andersson and K. Bletsas. Sporadic multiprocessor scheduling with few preemptions. In *Euromicro Conference on Real-Time Systems (ECRTS)*, pages 243–252, 2008.

- [2] B. Andersson and J. Jonsson. Fixed-priority preemptive multiprocessor scheduling: to partition or not to partition. In *Proceedings of the International Conference on Real-Time Computing Systems and Applications*, 2000.

- [3] A. Burns, R.I. Davis, P. Wang, and F. Zhang. Partitioned edf scheduling for multiprocessors using a C=D scheme. In *Proceedings of 18th International Conference on Real-Time and Network Systems (RTNS)*, pages 169–178, 2010.

- [4] A. Burns and A.J. Wellings. Dispatching domains for multiprocessor platforms and their representation in Ada. In J. Real and T. Vardanega, editors, *Proceedings of Reliable Software Technologies - Ada-Europe 2010*, volume LNCS 6106, pages 41–53. Springer, 2010.

- [5] A. Burns and A.J. Wellings. Multiprocessor systems: Session summary. *Ada Letters Proceedings of the 14th International Workshop on Real-Time Ada Issues (IRTAW 14)*, XXX(1):16–25, 2010.

- [6] A. Burns and A.J. Wellings. Supporting execution on multiprocessor platforms. *Ada Letters Proceedings of the 14th International Workshop on Real-Time Ada Issues (IRTAW 14)*, XXX(1):16–25, 2010.

- [7] J. Real and S. Mitchell. Beyond Ada 2005 session report. In *Proceedings of IRTAW 13, Ada Letters, XXVII*(2), pages 124–126, 2007.

- [8] J. Ruiz. Towards a ravenscar extension for multiprocessor systems. *Ada Letters Proceedings of the 14th International Workshop on Real-Time Ada Issues (IRTAW 14)*, XXX(1):86–90, 2010.

- [9] K. Shinpei and Y. Nobuyuki. Portioned EDF-based scheduling on multiprocessors. In EMSOFT, pages 139–148, 2008.

- [10] M. Ward and N.C Audsley. Suggestions for stream based parallel systems in Ada. In *Proceedings of IRTAW 13*, *Ada Letters*, *XXVII*(2), pages 33–138, 2007.

- [11] A.J. Wellings and A. Burns. Beyond Ada 2005: allocating tasks to processors in SMP systems. In *Proceedings of IRTAW 13, Ada Letters, XXVII(2)*, pages 75–81, 2007.

- [12] A.J. Wellings, A.H. Malik, N.C. Audsley, and A. Burns. Ada and cc-NUMA architectures. what can be achieved with Ada 2005? *Ada Letters Proceedings of the 14th International Workshop on Real-Time Ada Issues (IRTAW 14)*, XXX(1):125–134, 2010.

#### TTF-Ravenscar: A Profile to Support Reliable High-Integrity Multiprocessor Ada Applications

A. Burns, A.J. Wellings and A.H. Malik Department of Computer Science, University of York Heslington, York YO10 5GH, UK (burns,andy,haseeb)@cs.york.ac.uk

#### **Abstract**

Although the Ravenscar profile of Ada has achieved a measure of success in the development of high-integrity system, it is often criticised for not having enough expressive power to deal with common real-time programming patterns. This has led to a call for more facilities to be added to the profile. These have been turned down by the Ada standardization body for fear of "feature creep" and the lack of clear and consistent motivation. This paper proposes a coherent profile to support the construction of fault-tolerant high-integrity real-time programs.

#### 1 Introduction

The success of the Ravenscar profile has resulted in the call for more facilities to be added to the profile [10, 11, 13]. However, often these facilities do not have an underlying coherent model and have been turned down by the Ada standardization body for fear of "feature creep".

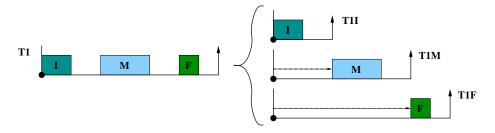

The alternative approach to providing a more expressive profile is to start from the computation model that Ravenscar<sup>1</sup> was intended to support and to extend that model. A new profile can then be defined to support this new model. In this paper, we propose an augmented Ravenscar profile whose goal is to support applications that are required to tolerate timing faults (we define the term TTF-Ravenscar for this profile). The motivations for defining a new profile come from:

- the increased use of multicore platforms in high-integrity systems and the accompanying greater uncertainty that is present with current timing (schedulability and worst-case execution) analysis for these platforms,

- the desire to use a Ravenscar-like sets of features (i.e. not the full language) to program high-integrity systems that can identify and respond to faults even if full fault recovery is not possible (as this typically requires use of language features only available via the full language).

Any new profile should ideally retain the key properties of Ravenscar – that is, its run-time support system should be small, efficient and potentially certifiable.

The paper is structured as follows. Section 2 discusses our assumptions and presents our fault-tolerance framework within which programs execute. Section 3 then considers the use of Ravenscar within this framework and identifies where support is lacking. The TTF-Ravenscar profile is then defined and discussed in section 4. Finally conclusions are drawn.

#### 2 Assumptions

Before suggesting any new profile that addresses fault-tolerance issues, it is important to define the failure assumptions and the overall framework within which fault tolerance is to be provided. Here, we assume failures in the underlying execution

<sup>&</sup>lt;sup>1</sup>In this paper, we will use the term Ravenscar to indicate the subset of Ada that is allowed when conforming to the Ada Ravenscar profile.

platform (processor, memory and bus) are handled outside of the Ada program, and that they are either masked or result in the whole system crashing: hence we assume crash failures [5] only. We use the traditional definitions for failures, errors and faults: **failures** result from unexpected problems internal to the system which ultimately manifest themselves in the system's external behaviour; these problems are called **errors** and their mechanical or algorithmic cause are termed **faults**. A fault is **active** when it produces an error, until this point it is **dormant**. Once produced, the error can be transformed into other errors via the computational progress through the system. Eventually, the error manifests itself at the boundaries of the system causing a service delivery to fail [3]. This failure, then becomes a fault in any other systems that uses the first system as a component. The fault-error-failure-fault chain is one of the underlying assumptions of fault-tolerance.

According to the Anderson and Lee framework [1], the provision of software dynamic redundance consists of the following phases [4, 1].

- 1. **Error detection** A fault will ultimately manifest itself in the form of an error; no fault tolerance scheme can be utilized until that error is detected.

- 2. **Damage confinement and assessment** When an error has been detected, it is necessary to decide to what extent the system has been corrupted (this is often called *error diagnosis*); the delay between a fault occurring and the detection of the associated error means that erroneous information could have spread throughout the system.

- 3. **Error recovery** Error recovery techniques aim to transform the corrupted system into a state from which it can continue its normal operation (perhaps with degraded functionality).

- 4. **Fault treatment and continued service** An error is a symptom of a fault; although the damage may have been repaired, the fault may still exist, and therefore the error may recur unless some form of maintenance is undertaken.

From our perspective, we are concerned with tolerating timing faults. In this case, the above phases can be re-interpreted as follows [4].

- 1. **Error detection** Most timing faults will eventually manifest themselves in the form of missed deadlines.

- 2. **Damage confinement and assessment** When deadlines have been missed, it is necessary to decide which tasks in the system are at fault. Ideally, confinement techniques should ensure that only faulty tasks miss their deadlines.

- 3. **Error recovery** The response to deadline misses requires that the application undertakes some forward error recovery.

- 4. **Fault treatment and continued service** Timing errors often result from transient overloads. Hence they can often be ignored. However, persistent deadline misses may indicate more serious problems and require some form of maintenance to be undertaken.

The faults that may result in missed deadlines include the following [4]:

- worst-case execution time (WCET) calculations were inaccurate (optimistic rather than pessimistic),

- blocking times were underestimated,

- assumptions made in the schedulability checker were not valid,

- the schedulability checker itself had an error,

- the scheduling algorithm could not cope with a load even though it is theoretically schedulable,

- the system is working outside its design parameters, for example sporadic events occurring more frequently than was assumed in the schedulability analysis.

Assuming the schedulability analysis is correct, the following chains are possible in the context of priority-based systems [7]:

1. Fault (in task  $\tau_i$ 's WCET calculation or assumptions)  $\rightarrow$  error (overrun of  $\tau_i$ 's WCET)  $\rightarrow$  error propagation (deadline miss of  $\tau_i$ )  $\rightarrow$  failure (to deliver service in a timely manner);

- 2. Fault (in task  $\tau_i$ 's WCET calculation or assumptions)  $\rightarrow$  error (overrun of  $\tau_i$ 's WCET)  $\rightarrow$  error propagation (greater interference on lower priority tasks)  $\rightarrow$  error propagation (deadline miss of lower priority tasks)  $\rightarrow$  failure (to deliver service in a timely manner);

- 3. Fault (in task  $\tau_i$ 's minimum inter-arrival time assumptions)  $\rightarrow error$  (greater computation requirement for  $\tau_i$ )  $\rightarrow error$  propagation (deadline miss of  $\tau_i$ )  $\rightarrow$  failure (to deliver service in a timely manner);

- 4. Fault (in task  $\tau_i$ 's minimum inter-arrival time assumptions)  $\rightarrow error$  (greater interference on lower priority tasks)  $\rightarrow error$  propagation (deadline miss of lower priority tasks)  $\rightarrow failure$  (to deliver service in a timely manner);

- 5. Fault (in task  $\tau_i$ 's WCET calculation or assumptions when using a shared resource)  $\rightarrow$  error (overrun of  $\tau_i$ 's resource usage)  $\rightarrow$  error propagation (greater blocking time of higher priority tasks sharing the resource)  $\rightarrow$  error propagation (deadline miss of higher priority tasks)  $\rightarrow$  failure (to deliver service in a timely manner).

To be tolerant of timing faults, it is necessary to be able to detect:

- miss of a deadline the final error in all the above error propagation chains;

- overrun of a worst-case execution time potentially causing the task and/or lower priority tasks to miss their deadlines (error chains 1 and 2);

- a sporadic event occurring more often than predicted potentially causing the task and/or lower priority tasks to miss their deadlines (error chains 3 and 4);

- overrun in the usage of a resource potentially causing higher priority tasks to miss their deadlines (error chain 5).

Of course the last three error conditions do not necessary indicate that deadlines will be missed; for example, an overrun of WCET in one task might be compensated by a sporadic event occurring less often than the maximum allowed. Hence, the damage confinement and assessment phase of providing fault tolerance must determine what actions to take.

The following section will discuss the extent to which Ravenscar can support: error detection mechanisms for the above timing faults, possible error confinement approaches, and strategies for recovery. Fault treatment typically involves maintenance, which is a topic outside the scope of this paper.

#### 3 Ravenscar and Dynamic Software Fault Tolerance

In section 2, the class of faults that could result in an application missing its deadline were identified. This section first considers, the Ravenscar facilities that allow the resulting errors to be detected. This is followed by a brief discussion on damage/error confinement. Finally, the error recovery phase is considered.

#### 3.1 Error detection

From a timing perspective, there are three primitive errors that can result in a deadline miss.

- 1. WCET (Budget) overrun Modern multicore processors make accurate and tight WCET analysis extremely difficult. To reflect this, we will assume that each Ada task has a CPU budget and not be concerned with whether this a worst-case measure. It will be up to the application to decide how to respond to budget overrun during its error recovery phase.

- Ravenscar supports execution-time clocks but not the Ada. Execution\_Time. Timers package. Hence, the only possible approach to detect budget overrun is to poll for it. Clearly, this is very inefficient and, in practice, the overrun is likely to be detected well after the fact.

- 2. Overrun of sporadic events A sporadic event firing more frequently than anticipated can have an enormous impact on a system attempting to meet hard deadlines. Where the event is the result of an interrupt, the consequences can be potentially devastating.

Ada has no notion of a release event (job) so any detection of this overrun condition must be provided by the application. In general, this can be achieved using protected objects and timers as illustrated in Section 13.4.1 of Burns and Wellings [4]. Note that this code is Ravenscar-compliant.

3. Overrun of worst-case blocking time – In Ada, tasks cannot self-suspend while hold protected object locks. Assuming the protected-object usage has been accurately determined during the analysis phase, the only way a blocking overrun can occur is if the budget allocated to each protected action overruns, or blocking has been introduced by the Ada runtime environment. Support for detecting blocking overruns is traditionally not found in real-time operating systems, and consequently is not supported by Ada. The error will, therefore, propagate and either a) be transformed into a budget overrun, or b) go undetected until its affect is lost or c) result in a missed deadline. As an aside, Ada does not define the task that executes an entry body in a protected object. Hence, calculating the execution time of a protected procedure, which results in an entry becoming open, may require that entry and (in the general case) several other entries to be taken into account.

Given no support in Ada, and the catch-all detection capability of a missed deadline, we will not consider this case further.

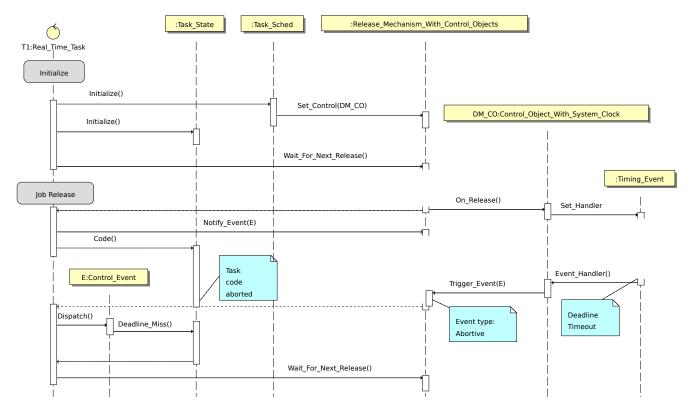

The fall-back position for all timing faults is to detect a deadline miss. In Ravenscar, a deadline miss can be detected by using timers attached to the Real-Time clock.

#### 3.2 Damage confinement

The role of damage confinement of time-related faults is to prevent propagation of the resulting errors to other components in the system. There are two aspects of this that can be identified.

- Protecting the system from the impact of sporadic task overruns and unbounded aperiodic activities. The problem of overruns in sporadic objects and unbounded demand on the processor's time from aperiodic activities is usually handled by *Aperiodic Servers* such as *Sporadic Servers* and *Deferrable Servers*.

- Supporting composability and temporal isolations. When composing systems of multiple components, whether dynamically or statically, it is often required that each component be isolated from one another. Typically, this is achieved by hierarchy schedulers and reservation-based systems. Usually, two levels of scheduling are used. A global (top-level) scheduler and multiple application-level (second-level) scheduler. Usually, the application-level scheduler is also called called a Server or Execution-time Server or Group Server.

Although the above confinement techniques are similar, they have slightly different emphasis. For temporal isolation, the key requirement is that the Group Server be *guaranteed its budget each period*. To support sporadic and aperiodic execution, it is sufficient that the server *consumes no more than its budget each period*.

To implement both execution-time servers and aperiodic server typically requires a group budget facility. Ravenscar does not support the Ada. Execution\_Time.Group\_Budget package.

#### 3.3 Error recovery

The greater the accuracy by which the fault and its resulting error can be detected and confined to the errant task, the easier it is to program recovery. Hence detecting budget overrun in a task indicates that it is that tasks that has the fault. In contrast, detecting deadline miss in a task does not necessarily mean that task is at fault.

This subsection considers the appropriate strategies for hard (deadlines must be met), soft (deadlines can occasional be missed and there is still some value in delivering a service late) and firm (deadlines can occasional be missed but there is no value in delivering a service late).

#### 3.3.1 Strategies for handling budget overrun

Once detected, the task response will depend on whether it is a hard, soft or firm deadline.

**Budget overrun in hard real-time tasks** One possibility, is that the WCET values used in the schedulability analysis consists of the addition of two components. The first is the time allocated for the primary algorithm and the second is the time for recovery (assuming a fault hypothesis of a single failure per task per release). The first time is the time that is used by the system when monitoring. When this time passes, recovery occurs and the alternative algorithm can be executed. This can either be within the same task and the budget increased, or by releasing a dedicated recovery task. Typically, these alternative algorithms try to provide a degraded service. Another possibility is simply to do nothing. This assumes that there is enough slack in the system for the task (and other lower priority tasks) to still meet their deadlines.

**Budget overruns in soft/firm real-time tasks** Typically overruns in soft and firm real-time tasks can be ignored if the isolation techniques guarantee the capacity needed for the hard real-time tasks. Alternatively, the tasks priorities can be lowered, or the current releases can be terminated and the tasks re-released when their next release event occurs.

#### 3.3.2 Strategies for handling sporadic event overruns

There are several responses to the violation of minimum inter-arrival time of a sporadic task: the release event can be ignore, an exception can be raised, the last event can be overwritten, (if it has not already been acted upon) or the actual release of the thread can be delayed until the MIT<sup>2</sup> has passed. Of course, the violation could be ignored and the task release allowed.

#### 3.3.3 Strategies for handling deadline misses

Although the early identification of potential timing problems facilitate damage assessment, many real-time systems just focus on the recovery from missed deadlines. Several strategies are possible.

**Deadline miss of hard real-time tasks** – Again it is possible to set two deadlines for each task. An early deadline whose miss will cause the invocation of forward or backward error recovery. A later deadline is the deadline used by the schedulability test. In both cases, the recovery should aim to produce a degraded service for the task.

**Deadline miss of soft real-time task** – Typically this can be ignored and treated as a transient overload situation. A count of missed deadlines can be maintained, and when it passes a certain threshold a health monitoring system can be informed.

**Deadline miss of a firm real-time task** – As a firm task produces no value passed its deadline, its current release can be terminated. A count of terminated release can be maintained, and when it passes a certain threshold a health monitoring system can be informed.

#### 3.3.4 Mode changes and event-based reconfiguration

In the above discussions, it has generally been assumed that a missed deadline and other timing errors can be dealt with by the task that is actually responsible for the problem. This is not always the case. Often the consequences of a timing error are as follows.

- Other tasks must alter their deadlines or even terminate what they are doing.

- New tasks may need to be started.

- Critically important computation may require more processor time than is currently available; to obtain the extra time, other less significant tasks may need to be 'suspended'.

- Tasks may need to be 'interrupted' in order to undertake one of the following (typically):

- immediately return their best results they have obtained so far;

- change to quicker (but presumably less accurate) algorithms;

- forget what they are presently doing and become ready to take new instructions: 'restart without reload'.

These actions are sometimes known as event-based reconfiguration.

Some systems may additionally enter anticipated situations in which deadlines are liable to be missed. A good illustration of this is found in systems that experience *mode changes*. This is where some event in the environment occurs which results in certain computations that have already been initialized, no longer being required. If the system were to complete these computations then other deadlines would be missed; it is thus necessary to terminate prematurely the tasks that contain the computations.

To perform event-based reconfiguration and mode changes requires communication between the tasks concerned. Due to the asynchronous nature of this communication, it is necessary to use the asynchronous notification mechanisms. Any reconfiguration may also require tasks to be moved between processors in order to balance the load.

<sup>&</sup>lt;sup>2</sup>Minimum Inter-arrival Time.

#### 3.3.5 Ravenscar and error recovery

There are several common techniques that are used to implement the above error-recovery strategies

- 1. Reduce the priority of the task to a priority level where it will not jeopardize the execution of other tasks.

- Ravenscar does not support the Ada. Dynamic\_Priorities package.

- 2. Move a task from one processor to another.

- Ravenscar does not support the System. Multiprocessor package, and its associated aspects.

- 3. Suspend the task completely.

- Ravenscar does not support the Ada . Asynchronous\_Task\_Control package.

- 4. Start a new task.

- Ravenscar does not support the dynamic creation of tasks, so all tasks must be created during the initialization phase. They can then queue on a mode changer (error recovery) protected object waiting for their mode to become active. Unfortunately, multiple tasks cannot be placed on the same entry queue. This results in obfuscated code, the problem is compounded by Ravenscar not supporting multiple entries in the same protected objects.

- 5. Request an asynchronous transfer of control in the task and then, possibly, also change its priority level.

- Ravenscar does not support the select-then-abort facility.

- 6. Terminate the current release (job) of the task and allow it to start afresh at the next release.

- Ada does not recognise the notion of releases. Hence there are no direct facilities to allow this. It has to be implemented by the program. The only way to do this would be to poll for the termination request.

#### 4 Supporting a TTF-Ravenscar Profile

To make it worthwhile to define a new profile, there must be a clear application need, a computational model that reflect this need, and an implementation strategy that leads to a run-time footprint significantly smaller than that needed by the full language. Earlier is this paper we have attempted to define a need (to tolerate timing faults) and a set of facilities that together form a coherent model whilst still requiring a run-time footprint much closer to Ravenscar than the full Ada language.

However, to be successful, any proposed new profile must also be easily implementable on a wide range of current operating system. In the past, we have always used the POSIX standard as our measure of wide-spread support. However, the POSIX standards have been a bit slow responding to the increase in use of multicore/multiprocessor platforms. For this reason, we use Linux (and its various patches) as our measure.

#### 4.1 Linux support relevant to the proposed profile

Linux was never designed to support real-time systems. Early versions of the Linux kernel were non-preemptible i.e. any task running inside a kernel (or a kernel driver) needed to finish its execution before anything else was allowed to execute [12]. Linux 2.0 supported symmetric multiprocessors by using a single spin lock (the big kernel lock) which allowed only one task to be running kernel code at one time. Later, locks were distributed based on critical regions rather than having a single lock for the whole kernel. However, any task inside the critical region was still non-preemptible and response times were still very high. The realtime-preempt patch was included in the mainline kernel in Linux 2.6.18<sup>3</sup> as a configuration option; it tries to minimize the amount of non-preemptible code.

On multiprocessors, ideally the OS should provide support for different scheduling policies from fully partitioned to global scheduling. In Linux, each processor has its own run queue. Once a thread is allocated to a processor it stays in its run queue until it is either moved to another processor by changing its affinity or through load balancing. Although Linux does not have a single queue for multiple processors for true global scheduling, however, it uses load balancing on real time tasks to make sure that the highest priority threads present in all the run queues are running at any particular instant of time [2]. When there is more than one real time thread in a run-queue, the lower priority real time thread is migrated to a CPU on which it can run. This migration happens at the following events:

<sup>&</sup>lt;sup>3</sup>http://www.Linuxfordevices.com/c/a/News/Linux-kernel-gains-new-realtime-support/

- 1. a real time thread becomes schedulable, however, it finds a higher priority thread already running in the run-queue on which it has been allocated. In such a case it is pushed to another run queue where it can run;

- 2. when a task is suspended (or completes) on one processor (processor A), and a task exists in the run queue of another processor (processor B) with a higher priority than the highest priority in processor A's queue, the kernel pulls the higher priority task from B's queue to A's queue, and the higher priority task is dispatched.

However, the migration does respect the affinities of the tasks and any such migrations are not allowed where the CPU is out of the affinity set of the task.

In Linux, control groups [9] provide a mechanism to partition groups of tasks and then manage resources allocated to each partition. Control group (cgroup) is a file system, where tasks can be added and then be arranged hierarchically. By default all tasks belong to the root cgroup. Each resource (CPU, memory etc.) has an associated controller which limits resources to tasks based on the cgroup they belong to.

Building the mainline kernel by enabling the CONFIG\_RT\_GROUP\_SCHED option, provides the support for real-time group scheduling. The real-time group scheduling can be used along with the cgroup filesystem to provide group budget for a set of tasks(process/threads). The real time group scheduling allows explicit allocation of CPU bandwidth to task groups [6]. The bandwidth can be set by the following two parameters

- 1. cpu.rt\_runtime\_us to set the budget of the task group

- 2. cpu.rt\_period\_us to set the period of the task group

In every period T, the group is allocated the budget. Once the budget expires, the group is blocked until the arrival of the next period. In Linux, the scheduler\_tick function is called periodically after a time period T which is called by a high resolution timer. This function maintains the different CPUs accounting parameters and checks for budget exhaustion. On each scheduling event (at the scheduler\_tick, task deactivation, task pre-emption) the collective execution times of all tasks are compared to the budget value until it exceeds the budget at which point all tasks are descheduled.

A sporadic server patch has also been presented in [8] with minimum changes to the real-time group scheduling of Linux. The changes mainly involve behaviour of threads; instead of blocking, threads are re-entered in a lower priority queue once the budget has expired. It also makes changes to how the budget is replenished after each period.

#### 4.2 The proposed TTF-Ravenscar profile

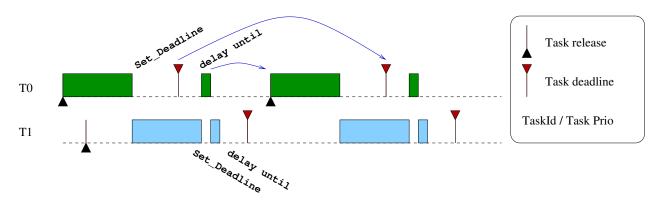

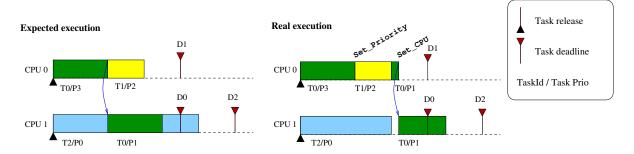

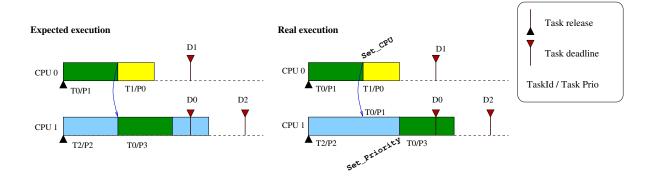

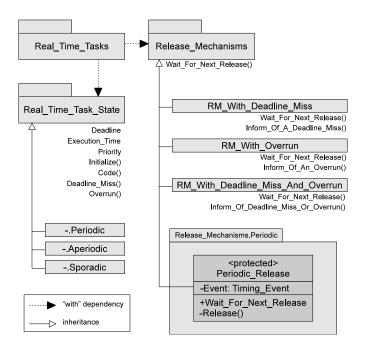

In section 3, several Ada facilities were needed that were not available in the Ravenscar. In this section, we discuss the feasibility of an augmented Ravenscar profile and whether the added functionality is supported by Linux.